VHDL-haastattelukysymyksen pitäisi johtaa VHDL-koodiin.

Minulla oli tilaisuus löytää ghdl llvm -taustavirhe Dave Tweedin tilasiirtotaulukon toteutuksella, jossa ghdlin kirjoittaja tislasi toteutuksen funktiossa 17 riviin:

-tyyppi on (r0, r1, r2, r3, r4); - loput arvot

funktio mod5 (osinko: bit_vektori) palauttaa loogisen arvon

type stay_array on matriisin (NBITS alas 0) jäännöksiä;

tyypin haara on jäännösten taulukko (jäännökset, bitti);

vakio br_table: haara: = (r0 = > ('0' = > r0, '1' = > r1),

r1 = > ('0' = > r2, '1' = > r3),

r2 = > ('0' = > r4, '1' = > r0),

r3 = > ('0' = > r1, '1' = > r2),

r4 = > ('0' = > r3, '1' = > r4)

);

muuttujan loppuosa: jäljellä: = r0;

muuttuja tbit: bit_vector (NBITS - 1 alas 0): = osinko;

alkaa

i: lle osingon pituudessa - 1 alaspäin 0 silmukkaan

jäännös: = br_table (loppu, tbit (i));

loppusilmukka;

paluu jäännös = r0;

lopputoiminto;

Liittyvä testitapaus on melko pieni, mikä helpottaa virheenkorjausta ja käyttää VHDL: n kanssa yhteensopivia tilanimiä luetelluissa tyypeissä:

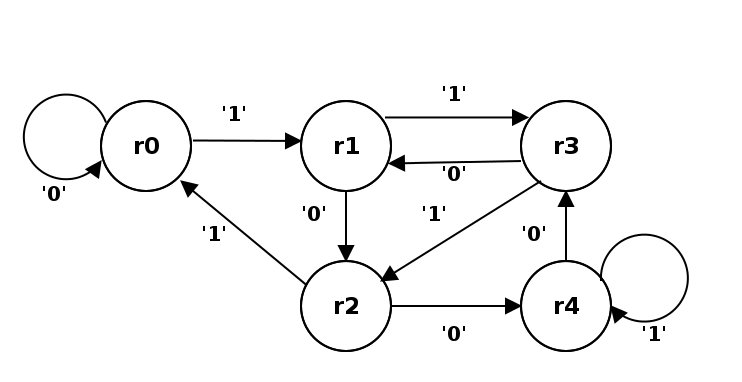

(luotu Dia: llä)

(luotu Dia: llä)

Ajatuksena on, että toiminto (tai jopa esimerkki 27 rivin VHDL-ohjelmasta) on riittävän lyhyt VHDL-vastauksen kirjoittamiseksi haastattelun aikana. Ei tarvitse huolehtia haastattelukysymyksen pilaamisesta, joka vaatii sekä tiedon että taitojen osoittamista, haastateltavan odotetaan puolustavan toteutusta, kun hänet kysytään.

(Llvm-taustavirhe on korjattu aiemmin 1f5df6e -sovelluksessa.)

Yksi huomioitavista asioista on tilansiirtotaulukko, joka kertoo meille myös, missä osamääräbitti olisi '1', joka näkyy siirtymällä tilaan, jolla on pienempi jäännösarvo (tai molemmat siirtymät ryhmälle r4), kun vähennetään 5 osinko. Se voidaan koodata erilliseen taulukkoon (tai tietuetyyppiseen taulukkoon, joka näyttää hankalalta). Teemme tämän historiallisesti grafiikkalaitteissa, jotka käsittelevät 5 pikselin kerrannaisia vaakanäyttöresoluutioita

Näin saat div / mod5: n, joka tuottaa osamäärän ja loput:

kirjasto ieee;

käytä ieee.std_logic_1164.all;

kokonaisuus divmod5 on

yleinen (

Huom: luonnollinen: = 13

);

satama (

clk: in std_logic;

osinko: std_logic_vectorissa (NBITS - 1 alas 0);

kuormitus: in std_logic;

osamäärä: out std_logic_vector (NBITS - 3 alas 0);

loppuosa: out std_logic_vector (2 alas 0);

remzero: out std_logic

);

loppuyksikkö;

divmod5-arkkitehtuurin foo on

tyypin jäännökset ovat (r0, r1, r2, r3, r4); - loput arvot

type stay_array on matriisin (NBITS alas 0) jäännöksiä;

signaalin jäännös: pysy_kuvaaja: = (muut = > r0);

signaalin dividendreg: std_logic_vector (NBITS - 1 alas 0);

signaalin lainausmerkki: std_logic_vector (NBITS - 3 alas 0);

alkaa

rinnakkain:

i: lle NBITS: ssä - 1 alas 0: n generointiin

tyypin haara on jäännösten taulukko (jäännökset, bitti);

- Dave Tweedsin tilan siirtymätaulukko:

vakio br_table: haara: = (r0 = > ('0' = > r0, '1' = > r1),

r1 = > ('0' = > r2, '1' = > r3),

r2 = > ('0' = > r4, '1' = > r0),

r3 = > ('0' = > r1, '1' = > r2),

r4 = > ('0' = > r3, '1' = > r4)

);

tyyppi qt on taulukon (jäännökset, bitti) std_ulogic;

- Luo osamääräbittejä Dave Tweedsin tilakoneesta q_taulukon avulla.

- '1', kun loppuosa menee alempaan jäännökseen tai molemmille haaroille

- r4: stä. "0" kaikille muille haaroille.

vakio q_taulukko: qt: = (r0 = > (muut = > '0'),

r1 = > (muut = > '0'),

r2 = > ('0' = > '0', '1' = > '1'),

r3 = > (muut = > '1'),

r4 = > (muut = > '1')

);

signaalin tbit: bitti;

alkaa

tbit < = to_bit (dividendreg (i));

remaindr (i) < = br_taulukko (remaindr (i + 1), tbit);

do_quotient:

jos minä < quot'pituuden generoida

quot (i) < = q_taulukko (loppuindr (i + 1), tbit);

loppu generoida;

loppu generoida;

dividend_reg:

prosessi (clk)

alkaa

jos nouseva_reuna (clk) sitten

jos kuorma = '1' sitten

dividendreg < = osinko;

loppu Jos;

loppu Jos;

lopeta prosessi;

quotient_reg:

prosessi (clk)

alkaa

jos nouseva_reuna (clk) sitten

osamäärä < = quot;

loppu Jos;

lopeta prosessi;

loput:

prosessi (clk)

alkaa

jos nouseva_reuna (clk) sitten

remzero < = '0';

tapaus jäännös (0) on

kun r0 = >

loppuosa < = "000";

remzero < = '1';

kun r1 = >

loppuosa < = "001";

kun r2 = >

loppuosa < = "010";

kun r3 = >

loppuosa < = "011";

kun r4 = >

loppuosa < = "100";

lopputapaus;

loppu Jos;

lopeta prosessi;

loppuarkkitehtuuri;

kirjasto ieee;

käytä ieee.std_logic_1164.all;

käytä ieee.numeric_std.all;

kokonaisuus divmod5_tb on

loppuyksikkö;

divmod5_tb-arkkitehtuurin foo on

vakio NBITS: kokonaislukualue 0-13: = 8;

signaali clk: std_logic: = '0';

signaaliosinko: std_logic_vector (NBITS - 1 alas 0);

signaalin kuormitus: std_logic: = '0';

signaalin osamäärä: std_logic_vector (NBITS - 3 alas 0);

signaalin loppuosa: std_logic_vector (2 alas 0);

signaalin remzero: std_logic;

signaaliesimerkki: std_ulogic;

signaalinäyte: std_ulogic;

signaali tehty: looginen;

alkaa

DUT:

kokonaisuus work.divmod5

yleinen kartta (NBITS)

satamakartta (

clk = > clk,

osinko = > osinko,

kuorma = > kuorma,

osamäärä = >-osamäärä,

jäännös = > jäännös,

remzero = > remzero

);

KELLO:

käsitellä asiaa

alkaa

odota 5 ns;

clk < = ei clk;

jos valmis, viivästynyt (30 ns) sitten

odota;

loppu Jos;

lopeta prosessi;

ÄLKÖ:

käsitellä asiaa

alkaa

i: lle 0 - 2 ** NBITS - 1 silmukka

odota 10 ns;

osinko < = std_logic_vector (allekirjoittamaton (i, NBITS));

odota 10 ns;

kuormitus < = '1';

odota 10 ns;

kuorma < = '0';

loppusilmukka;

odota 15 ns;

tehty < = tosi;

odota;

lopeta prosessi;

NÄYTTEENOTTO:

prosessi (clk)

alkaa

jos nouseva_reuna (clk) sitten

psample < = kuorma;

näyte < = psample 4 ns jälkeen;

loppu Jos;

lopeta prosessi;

MONITORI:

prosessi (näyte)

muuttuja i: kokonaisluku;

muuttuja div5: kokonaisluku;

muuttuja rem5: kokonaisluku;

alkaa

jos nouseva_reuna (näyte) sitten

i: = kokonaisluku (allekirjoittamaton (osinko));

div5: = i / 5;

väitä div5 = allekirjoittamaton (osamäärä)

raportti LF & HT &

"i =" & kokonaisluku "kuva (i) &

"div 5 odotettavissa" & kokonaisluku -kuva (div5) &

"got" & kokonaislukukuva (to_integer (allekirjoittamaton (osamäärä)))

VAKAVUUSVIRHE;

rem5: = i mod 5;

väitä rem5 = allekirjoittamaton (loppu)

raportti LF & HT &

"i =" & kokonaisluku "kuva (i) &

"Rem 5 odotettu" & kokonaisluku'kuva (rem5) &

"got" & kokonaislukukuva (to_integer (allekirjoittamaton (loppuosa)))

VAKAVUUSVIRHE;

loppu Jos;

lopeta prosessi;

loppuarkkitehtuuri;

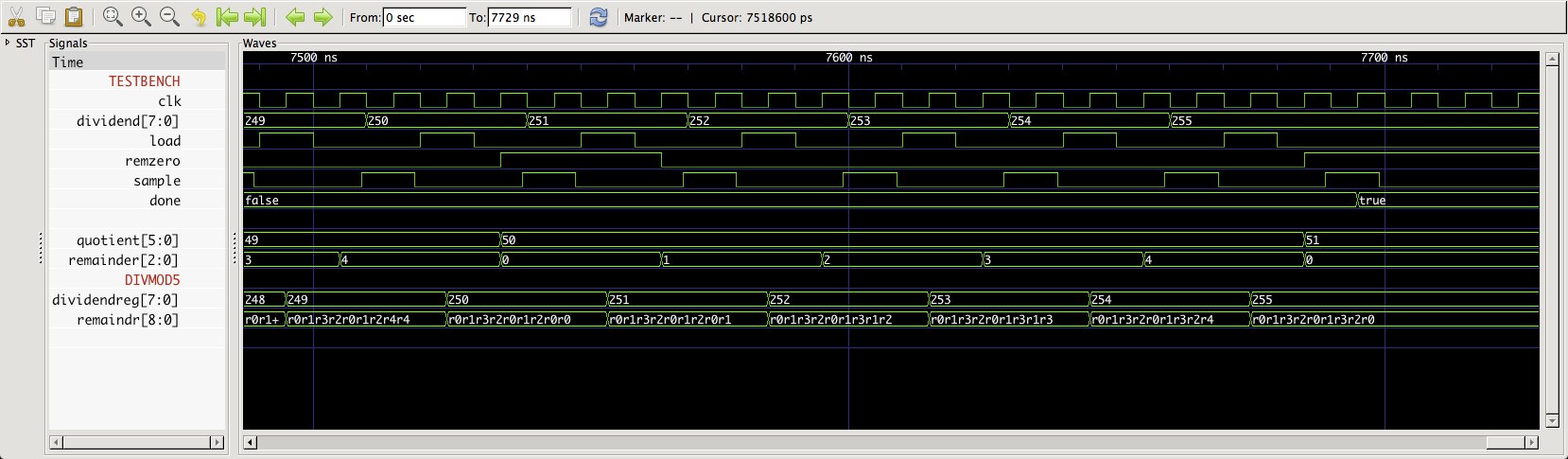

Toteutettu tässä generointilausekkeella, sisäinen generointilauseke, joka tuottaa osioibittejä. Remaindr-taulukko tarjoaa tilansiirtojäljen:

Kaikki ilman aritmeettista operaatiota.

On myös mahdollista toteuttaa menettelyssä ilman, että kaikki rekisterit hyödyntävät parametreja tilassa mode out. Se lähestyisi haastattelun vähimmäismäärää.

Kellotettu peräkkäinen toteutus vaatii bittilaskurin ja virtauksen ohjauksen (JK-kiikku ja pari porttia).

Aika / monimutkaisuus vaihtelee osinkojen koosta riippuen, mitä sinun todennäköisesti myös puolustetaan haastattelussa.