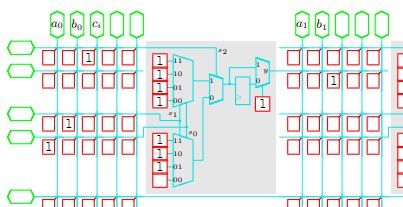

Vihreät laatikot ovat IO-nastoja, siniset viivat ovat johtoja, punaiset laatikot ovat kokoonpanobittejä ja harmaat laatikot ovat logiikkalohkoja. Punaiset laatikot voivat antaa vakiologiikan 0 tai logiikan 1 riippumatta siitä, mihin ne ovat yhteydessä.

Jokainen logiikkalohko toteuttaa 3 tulon, 1 lähdön hakutaulukon (kolmen tulon logiikkatasojen yhdistelmä määrittää, mikä kahdeksasta kokoonpanobitistä on valittu) ja siinä on ohitettava kiikku. Viestisi näyttää myös totuustaulukon, jonka LUT toteuttaa, osoittaen, mikä konfigurointibitti on valittu jokaiselle yhdistelmälle s0, s1 ja s2.

Esimerkiksi sinisten johtojen risteyksissä olevat punaiset laatikot on kytketty johtojen väliseen porttiin. Jos jokin näistä asetetaan arvoon 1, vaaka- ja pystylangat yhdistetään toisiinsa ja asetetaan arvoon 0, jolloin johdot ovat irti.

Sinun on kirjoitettava 1 tai 0 kuhunkin punaiseen ruutuun, jotta yläosassa olevien vihreiden ruutujen tulosignaalit lähetetään logiikkalohkojen läpi, jotka sinun on määritettävä tarvittavan logiikan toteuttamiseksi. toiminnon suorittamiseksi. Näyttää siltä, että he haluavat sinun lisäävän {a1, a0}, {b1, b0} ja ci yhteen.

Tässä on esimerkki 3-tuloisen TAI portin toteuttamisesta:

Kaikkien tyhjien ruutujen oletetaan olevan loogisia 0. Tämä vie 3 tuloa a0 b0 ja ci, laskee loogisen TAI ja antaa tuloksen vapaalle pinille. Tärkeimpiä huomioitavia asioita ovat se, kuinka konfigurointibitit ohjaavat pääsoportteja yhdistämään kolme tulosignaalia logiikkalohkon kolmeen sisääntuloon ja lähtö vapaaseen lähtönippiin, ja miten logiikkalohko toteuttaa TAI-toiminnon - 0, kun kaikki tulot ovat 0, muuten 1, kiikku ohitetaan.